# ET6930 - Constant Current Array LED Controller

## **General Description**

ET6930 is designed for LED display with 96 dots constant current driver. The standard I<sup>2</sup>C communication protocol is adopted. Internal integration of communication interface, data latch, LED constant current drive module. Especially suitable for small LED display driver, with high brightness, constant output current and other characteristics.

## Features

- Up to 96 LEDs are supported

- Support 1~12 scan application, the maximum application matrix is 8 ×12 (8 SEG × 12 GRID)

- Output constant current driver

- 8 levels of brightness adjustment

- I<sup>2</sup>C communication interface

- Built in RC oscillation

- Built in power on reset

- Package: SSOP24 (ET6930S)

## **Device Information**

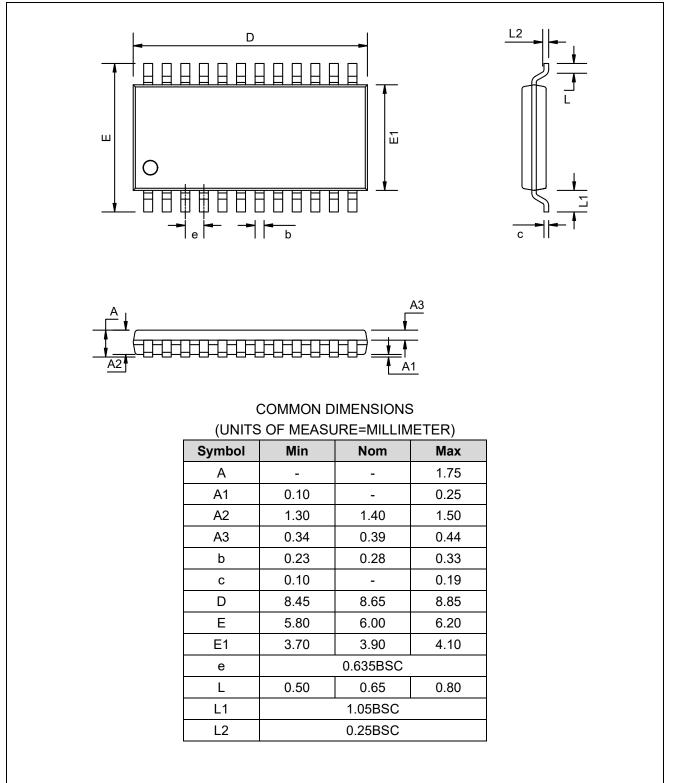

| Part No. | Package | Size           |

|----------|---------|----------------|

| ET6930S  | SSOP24  | 8.65mm × 6.0mm |

## Application

- Household appliances, Toy display

- Smart portable devices, Smart audio

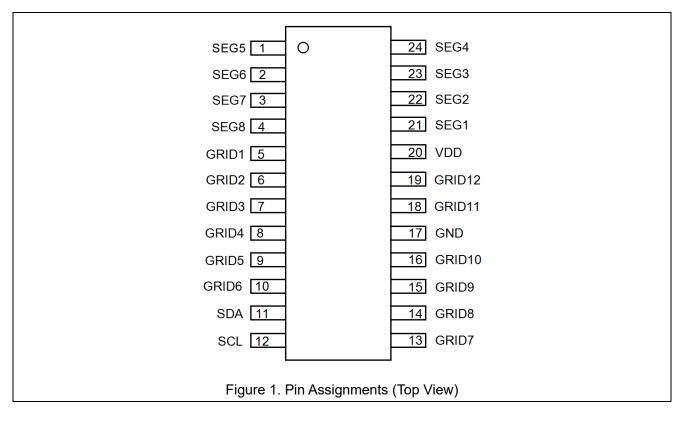

# **Pin Assignments**

## **Pin Description**

| Symbol         | Pin number       | Description                    |

|----------------|------------------|--------------------------------|

| SEG1~SEG8      | 21-24 1-4        | Segment output,                |

| 3EG1~3EG0      | 21~24,1~4        | connected to LED positive pole |

| GRID1~GRID12   | 5~10,13~16,18,19 | Grid output,                   |

| GRID I~GRID IZ | 5~10,15~10,10,19 | connected to LED negative pole |

| SDA            | 11               | l <sup>2</sup> C data input    |

| SCL            | 12               | I <sup>2</sup> C clock input   |

| GND            | 17               | Ground                         |

| VDD            | 20               | Power supply                   |

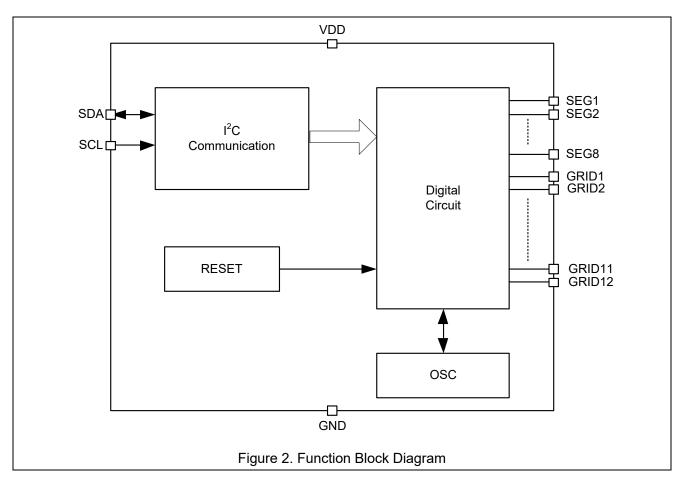

# **Function Block Diagram**

## **Functions Description**

#### Introduction

ET6930 is a constant current driver IC for LED display panel based on  $I^2C$  communication protocol. It supports up to 8 Segs × 12 Girds output, and can adjust the number of scanning Grids through register configuration, so as to obtain larger single point drive current.

The traditional LED display panel constant voltage drive IC, when the number of lit led changes or the power supply voltage changes, the current of a single LED will change, which will affect the display effect and ET6930 adopts the constant current drive design, when the display mode is configured, the current of each LED will be constant, and will not fluctuate due to the number of lit led changes or the power supply voltage changes.

## Serial Port Interface (I<sup>2</sup>C)

#### **Bus Interface**

MCU can transmit data with ET6930 each other through SDA and SCL port. SDA and SCL composite bus interface, and a pull-up resistor to the power supply should be connected.

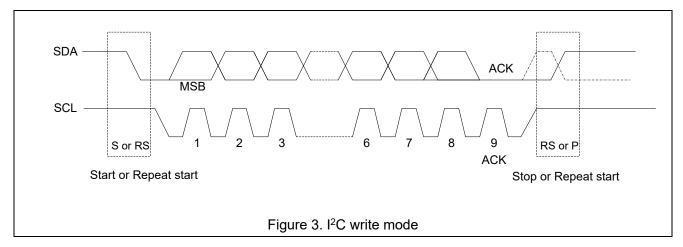

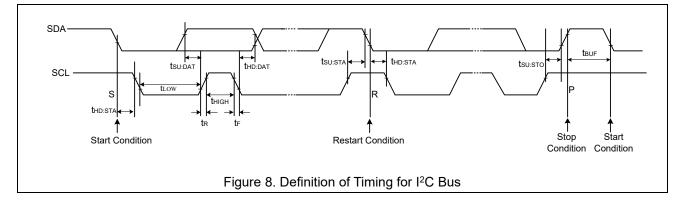

## **Data Validity**

When the SCL signal is HIGH, the data of SDA port is valid and stable. Only when the SCL signal is low, the level on the SDA port can be changed.

### Start (Re-start) and Stop Working Conditions

When the SCL signal is high, SDA signal from high to low represents start or re-start working conditions, while the SCL signal is high, SDA signal from low to high represents stop working conditions.

### Byte format

Each byte of data line contains 8 bits, which contains an acknowledge bit. The first data is transmitted MSB.

### Acknowledge

During the writing mode, ET6930 will send a low level response signal with one period width to the SDA port. During the reading mode, ET6930 will not send response signal and the host will send a high response signal one period width to the SDA.

Note: ACK=Acknowledge

MSB=Most Significant Bit

S=Start Conditions RS=Restart Conditions P=Stop Conditions

Fastest Transmission Speed =400KBITS/S

Restart: SDA-level turn over as expressed by the dashed line waveform

#### **Chip-Address**

| Chip-Address   | Description                  |

|----------------|------------------------------|

| 84H(10000100B) | Only write mode is supported |

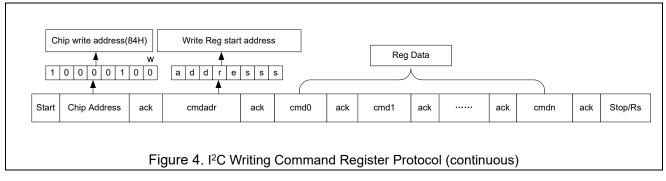

#### I<sup>2</sup>C Writing Command Register Interface Protocol (continuous):

• Start = Start Conditions

- Chip Address = Write register address = 10000100

- ack = Acknowledge from ET6930

- Write Reg start address byte = cmdadr (REG's 8bit address)

- ack = Acknowledge from ET6930

- Command Reg data 0=cmd0(Command data )

- ack = Acknowledge from ET6930

- .....

- Command Reg data n=cmdn(Command data )

- ack = Acknowledge from ET6930

- Stop/Rs=Stop Condition/Restart Condition

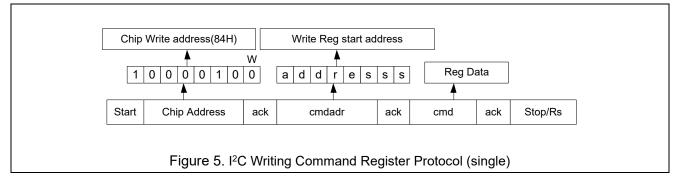

### I<sup>2</sup>C Writing Command Register Interface Protocol (single):

- Start =Start Conditions

- Chip Address = Write register address = 10000100

- ack = Acknowledge from ET6930

- Write Reg start address byte = cmdadr(REG's 8bit address)

- ack = Acknowledge from ET6930

- Command Reg data =cmd(Command data)

- ack = Acknowledge from ET6930

- Stop/Rs=Stop Condition/Restart Condition

## **Register Map**

| Addr    | Description             |

|---------|-------------------------|

| 00H~0BH | Display Data Register   |

| 10H~11H | Display Mode Register   |

| 12H     | Status Control Register |

## **Display Data Register**

These register stores the display data of ET6930, with the address from 00H to 0BH, a total of 12 byte units, corresponding to the LED lights of the matrix connected to the SEGn and GRIDn pins respectively.

| Addr | Parameter   | Description                                     | Defalt Value |

|------|-------------|-------------------------------------------------|--------------|

| 00H  | GRID1 Data  | Grid1data<7:0> Corresponding control SEG8~SEG1  | 00H          |

| 01H  | GRID2 Data  | Grid2data<7:0> Corresponding control SEG8~SEG1  | 00H          |

| 02H  | GRID3 Data  | Grid3data<7:0> Corresponding control SEG8~SEG1  | 00H          |

| 03H  | GRID4 Data  | Grid4data<7:0> Corresponding control SEG8~SEG1  | 00H          |

| 04H  | GRID5 Data  | Grid5data<7:0> Corresponding control SEG8~SEG1  | 00H          |

| 05H  | GRID6 Data  | Grid6data<7:0> Corresponding control SEG8~SEG1  | 00H          |

| 06H  | GRID7 Data  | Grid7data<7:0> Corresponding control SEG8~SEG1  | 00H          |

| 07H  | GRID8 Data  | Grid8data<7:0> Corresponding control SEG8~SEG1  | 00H          |

| 08H  | GRID9 Data  | Grid9data<7:0> Corresponding control SEG8~SEG1  | 00H          |

| 09H  | GRID10 Data | Grid10data<7:0> Corresponding control SEG8~SEG1 | 00H          |

| 0AH  | GRID11 Data | Grid11data<7:0> Corresponding control SEG8~SEG1 | 00H          |

| 0BH  | GRID12 Data | Grid12data<7:0> Corresponding control SEG8~SEG1 | 00H          |

## **Display Mode Register**

|      | Addr: 10h | Reset Register |         |        |             |                              |  |  |

|------|-----------|----------------|---------|--------|-------------|------------------------------|--|--|

| Addr | Bit       | Bit Name       | Default | Access | Description |                              |  |  |

|      | 7:4       | -              | 0000    | -      |             | -                            |  |  |

|      |           |                |         |        | SEG         | port output constant current |  |  |

|      |           | 0111           | 35mA    |        |             |                              |  |  |

| 10H  | 3:0       | Prightnoop     |         | W      | 0110        | 30.6mA                       |  |  |

|      | 3.0       | Brightness     | -       | vv     | 0101        | 26.25mA                      |  |  |

|      |           |                |         |        |             |                              |  |  |

|      |           |                |         |        | 0000        | 4.37mA                       |  |  |

|      | Addr: 11h |                |         |        | Reset       | Register                     |  |  |

| Addr | Bit       | Bit Name       | Default | Access |             | Description                  |  |  |

|      | 7:4       | -              | 0000    | -      |             | -                            |  |  |

|      |           |                |         |        | Num         | ber of valid GRID scan rows  |  |  |

|      |           |                |         |        | 1011        | 12 row                       |  |  |

| 11H  | 3:0       | Scan rows      |         | W      | 1010        | 11 row                       |  |  |

|      | 5.0       | Scarrows       | -       | vv     | 1001        | 10 row                       |  |  |

|      |           |                |         |        |             |                              |  |  |

|      |           |                |         |        | 0000        | 1 row                        |  |  |

*Note:* The display mode reg should be configured after power on.

### **Status Control Register**

|      | Addr: 12h  |          |         | Reset Register |             |                 |  |

|------|------------|----------|---------|----------------|-------------|-----------------|--|

| Addr | Bit        | Bit Name | Default | Access         | Description |                 |  |

|      | 0 Shutdown |          | 0       | W              | 0           | Shutdown        |  |

|      | 0          | Shutdown | 0       | vv             | 1           | Operating mode  |  |

| 12H  | 1          | Status   | 0       | W              | 0           | Display off     |  |

|      | 1          | control  |         | vv             | 1           | Display on      |  |

|      | 7:2        | -        | 000000  | -              | -           | Set to 0 please |  |

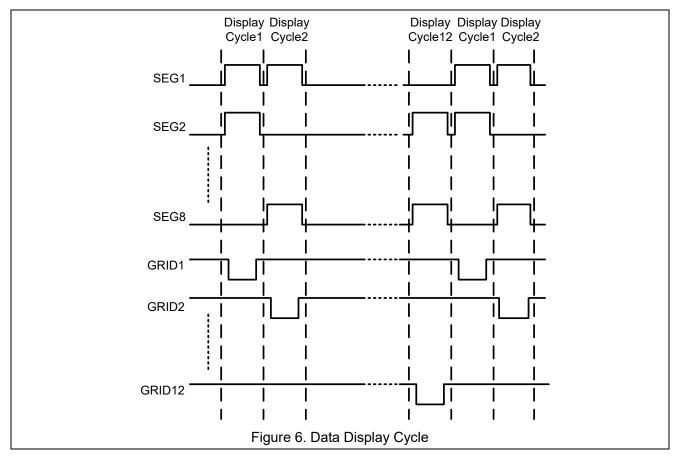

## **Display Cycle**

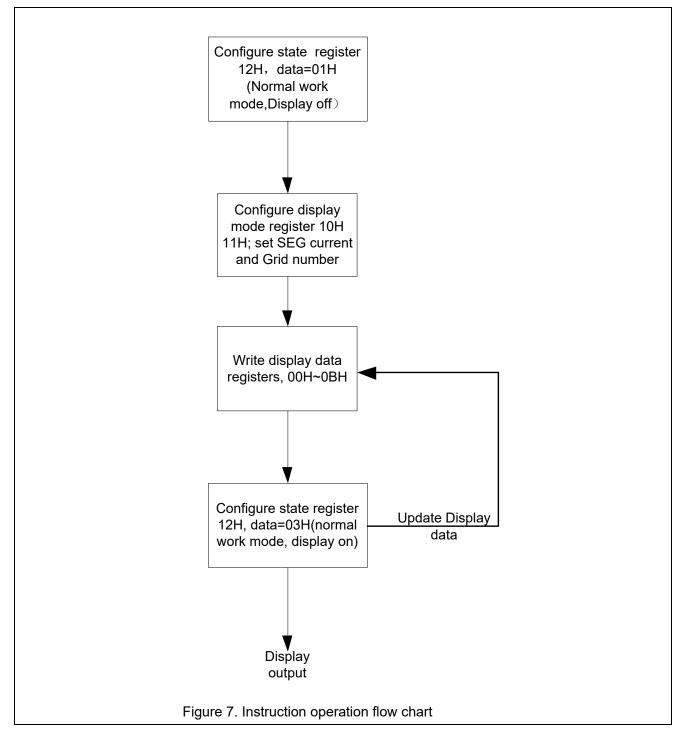

## **Command Sequence**

When power on for the first time, the state control register (12H) needs to be configured as 01h (that is, the circuit enters the normal working state).

Register writing order: state control register  $\rightarrow$  display mode register  $\rightarrow$  display data register  $\rightarrow$  state control register.

*Note:* Once bit0 of the state control register is set to 0, when re-writing data, be sure to configure the state control register to 01h before performing other operations.

# **Absolute Maximum Ratings**

(Unless otherwise noted ,T<sub>A</sub> =  $25^{\circ}C$ ,GND = 0V)

| Symbol           | Parameter name          | Condition                                 | Value      | Unit |

|------------------|-------------------------|-------------------------------------------|------------|------|

| Vdd              | Supply Voltage          |                                           | -0.3 ~ 6.0 | V    |

| los              | SEG drive current       | V <sub>DD</sub> =5V, T <sub>A</sub> =25°C | -72        | mA   |

| log              | GRID drive current      | V <sub>DD</sub> =5V, T <sub>A</sub> =25°C | 600        | mA   |

| PD               | Max power deterioration |                                           | 500        | mW   |

| θ <sub>JA</sub>  | Thermal resistance      | SSOP24                                    | 128        | °C/W |

| TA               | Junction temperature    |                                           | -40~150    | °C   |

| T <sub>STG</sub> | Store temperature       |                                           | -65~150    | °C   |

# **Recommended Operating Range**

(Unless otherwise noted  $,T_A = 25^{\circ}C,GND = 0V)$

| Symbol          | Parameter           | Min.        | Тур. | Max.               | Unit |

|-----------------|---------------------|-------------|------|--------------------|------|

| V <sub>DD</sub> | Supply Voltage      | 4.5         | 5.0  | 5.5                | V    |

| I <sub>DD</sub> | Operate current     |             |      | 250                | mA   |

| VIH             | Input high voltage  | $0.7V_{DD}$ | -    | V <sub>DD</sub>    | V    |

| VIL             | Input low voltage   | 0           | -    | 0.3V <sub>DD</sub> | V    |

| T <sub>A</sub>  | Operate temperature | -40         |      | 85                 | °C   |

## **DC Electrical Characteristics**

(Unless otherwise noted  $,T_A = 25^{\circ}C,GND = 0V$ )

| Symbol           | Parameter                     | Test Condition        | Min.               | Тур. | Max.               | Unit |

|------------------|-------------------------------|-----------------------|--------------------|------|--------------------|------|

|                  |                               | $V_{DD} = 5V$         |                    |      |                    |      |

| Iseg             | High level output current     | $V_0 = V_{DD}-1V$ ,   | -31.5              | -35  | -38.5              | mA   |

|                  |                               | '10H' write 0x7       |                    |      |                    |      |

| I <sub>OUT</sub> | Low level output current      | V <sub>0</sub> = 0.8V |                    | 560  | -                  | mA   |

| I <sub>IN</sub>  | Input current                 | $V_I = V_{DD}$        | -                  | -    | ±1                 | uA   |

| VIH              | High level input voltage      | SDA, SCL              | 0.7V <sub>DD</sub> | -    | -                  | V    |

| VIL              | Low level input voltage       | SDA, SCL              | -                  | -    | 0.3V <sub>DD</sub> | V    |

| V <sub>H</sub>   | Hysteresis voltage            | SDA, SCL              | -                  | 0.35 | -                  | V    |

| IDDDYN           | Dynamic current deterioration | No load, display off  | -                  | -    | 1                  | mA   |

| ISHDN            | Shutdown current              | Shutdown enable       |                    |      | 10                 | uA   |

-

## **AC Electrical Characteristics**

Symbol Parameter **Test Condition** Min. Тур. Max. T<sub>ZH1</sub> SEG1~8,CL=300pF **Rising time** 2 --0.5 T<sub>ZH2</sub> **Rising time** GRID1~12,CL=300pF --CL=300pF, SEGn, GRIDn

# (Unless otherwise noted, $V_{DD} = 5V$ , GND = 0V, $T_A = 25^{\circ}C$ )

## I<sup>2</sup>CTiming Characteristics

Dropping time

Tzн

(Unless otherwise noted,  $V_{DD} = 5V$ , GND = 0V, T<sub>A</sub>=25°C)

| Symbol              | Parameter                                               | Min | Тур                     | Max | Unit |

|---------------------|---------------------------------------------------------|-----|-------------------------|-----|------|

| F <sub>SCL</sub>    | SCL Clock Frequency                                     | -   | -                       | 400 | KHz  |

| t <sub>BUF</sub>    | Bus Free Time Between<br>STOP and START Condition       | 1.3 | -                       | -   | μs   |

| t <sub>HD:STA</sub> | t <sub>HD:STA</sub> Hold Time(Repeated) START Condition |     | -                       | -   | μs   |

| t <sub>LOW</sub>    | w Low Period of SCL Clock                               |     | -                       | -   | μs   |

| tніgн               | GH High Period of SCL Clock                             |     | -                       | -   | μs   |

| tsu:sta             | STA Setup Time for a Repeated START Condition           |     | -                       | -   | μs   |

| t <sub>HD:DAT</sub> | HD:DAT Data Hold Time                                   |     | -                       | 0.9 | μs   |

| t <sub>SU:DAT</sub> | SU:DAT Data Setup Time                                  |     | -                       | -   | ns   |

| t <sub>R</sub>      | Data Hold Time2                                         |     | 20+0.1Cb <sup>(1)</sup> | 300 | ns   |

| t⊧                  | Data Hold Time2                                         |     | 20+0.1Cb <sup>(1)</sup> | 300 | ns   |

| tsu:sто             | Setup Time for STOP Condition                           | 0.6 | -                       | -   | μs   |

Note1 : Cb=total capacitance of one bus line in PF.

## I<sup>2</sup>C Timing Waveform

Unit

us

us

us

120

-

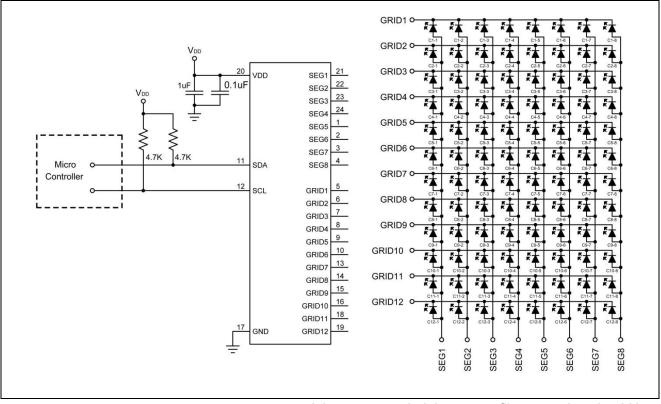

# **Application circuit**

*Note:* This application circuit is only for reference, It is recommended that power filter capacitor should be close to the  $V_{DD}$  pin as far as possible.

# Package

### SSOP24

# **Revision History and Checking Table**

| Version | Date       | Revision Item    | Modifier      | Function & Spec<br>Checking | Package & Tape<br>Checking |

|---------|------------|------------------|---------------|-----------------------------|----------------------------|

| 1.0     | 2020-02-24 | Original Version | Shi Liang Jun | Shi Liang Jun               | Zhu Jun Li                 |

| 1.1     | 2020-04-01 | Updated Form     | Shibo         | Shi Liang Jun               | Zhu Jun Li                 |

| 1.2     | 2022-07-23 | Updated Form     | Shibo         | Shi Liang Jun               | Liujy                      |