# Low-Power, RRIO, 1MHz Operational Amplifier for Cost-Sensitive Systems

#### **General Description**

ET85002 is a dual low-voltage (1.8 V to 5.5 V) operational amplifier with rail-to-rail input and output swing capabilities. ET85002 provides a cost-effective solution for space-constrained applications such as smoke detectors, wearable electronics, and small appliances where low-voltage operation and high capacitive-load drive are required. The capacitive-load drive is 500 pF and the resistive open-loop output impedance makes stabilization easier with much higher capacitive-loads. ET85002 features unity-gain stability, an integrated RFI and EMI rejection filter, and no-phase reversal in overdrive conditions.

ET85002 is specified for the extended industrial / automotive temperature range (-40°C to +125°C). ET85002 is available in SOP8 / MSOP8 / DFN8 packages.

#### **Features**

- Dual CMOS amplifier for low-cost applications

- Rail-to-rail input and output

- Low input offset voltage: ±0.4 mV

- Unity-gain bandwidth: 1 MHz

- Low broadband noise: 27 nV/√Hz

- Low input bias current: 5 pA

- Low quiescent current: 60 μA/Ch

- Unity-gain stable

- Internal RFI and EMI filter

- Operational at supply voltages as low as 1.8 V

- Easier to stabilize with higher capacitive load

- Extended temperature range: -40°C to 125°C

#### **Applications**

- Temperature sensors

- Sensor signal conditioning

- Power modules

- Active filters

- Low-side current sensing

#### **Device information**

| Part No. | Package   | MSL |

|----------|-----------|-----|

| ET85002M | SOP8      | 3   |

| ET85002U | MSOP8     | 3   |

| ET85002Y | DFN8(2×2) | 1   |

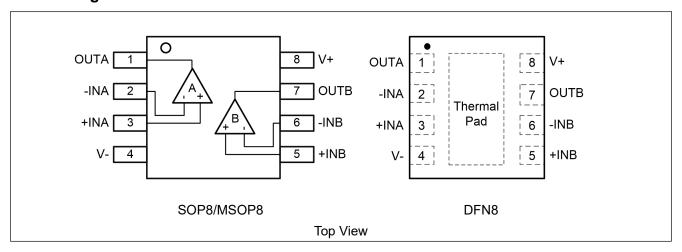

#### **Pin Configuration**

#### **Pin Function**

| Pin Number   | Complete | Descriptions        |

|--------------|----------|---------------------|

| ET85002M/U/Y | Symbol   | Descriptions        |

| 1,7          | OUT      | Output              |

| 4            | V-       | Negative supply     |

| 3,5          | +IN      | Non-inverting input |

| 2,6          | -IN      | Inverting input     |

| 8            | V+       | Positive supply     |

#### **Functional Description**

#### **Operating Voltage**

ET85002 is for operation from 1.8 V to 5.5 V. In addition, many specifications such as input offset voltage, quiescent current, offset current, and short circuit current apply from -40°C to 125°C.

#### Rail-to-Rail Input

The input common-mode voltage range extends 100 mV beyond the supply rails for the full supply voltage range of 1.8 V to 5.5 V. This performance is achieved with a complementary input stage.

#### Rail-to-Rail Output

Designed as a low-power, low-voltage operational amplifier, the ET85002 delivers a robust output drive capability. A class-AB output stage with common-source transistors achieves full rail-to-rail output swing

capability. For resistive loads of 10 k $\Omega$ , the output swings to within 20 mV of either supply rail, regardless of the applied power-supply voltage. Different load conditions change the ability of the amplifier to swing close to the rails.

#### **Device Functional Modes**

ET85002 has a single functional mode. The devices are powered on as long as the power-supply voltage is between 1.8 V ( $\pm 0.9$  V) and 5.5 V ( $\pm 2.75$  V).

#### **Absolute Maximum Ratings**

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are only stress ratings, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions are not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

| Parameter                                  | Rating                | Unit |

|--------------------------------------------|-----------------------|------|

| Supply Voltage <sup>(1)</sup> (V+) - (V-)  | 6.0                   | V    |

| Input Voltage                              | (V-)-0.3V to (V+)+0.3 | V    |

| Differential Input Voltage                 | (V+) - (V-)+0.2       | V    |

| ESD (Human Body Model)                     | ±2000                 | V    |

| Storage Temperature Range                  | -65 to +150           | °C   |

| Junction Temperature Range                 | -65 to +150           | °C   |

| Lead Temperature Range (Soldering, 60 sec) | 300                   | °C   |

| Operating Temperature Range                | -40 to +125           | °C   |

Note1: All voltage values, except differential voltage are with respect to network terminal.

#### **Recommended Operating Conditions**

| Parameter                               | Min | Max | Unit |

|-----------------------------------------|-----|-----|------|

| Supply Voltage (V <sub>S</sub> )        | 1.8 | 5.5 | V    |

| Operating Temperature (T <sub>A</sub> ) | -40 | 125 | °C   |

#### **Thermal Characteristics**

| Symbol            | Package   | Ratings                                                       | Value | Unit |

|-------------------|-----------|---------------------------------------------------------------|-------|------|

|                   | SOP8      | Thermal Characteristics,  Thermal Resistance, Junction-to-Air | 160   | °C/W |

| R <sub>θ</sub> ЈА | MSOP8     |                                                               | 200   | °C/W |

|                   | DFN8(2×2) | Thermal Resistance, Junetion-to-All                           | 160   | °C/W |

### **Electrical Characteristics**

$V_S$  = (V+) - (V-) = 1.8 V to 5.5 V (± 0.9 V to ± 2.75 V),  $T_A$  = 25°C,  $R_L$  = 10 k $\Omega$  connected to  $V_S/2$ , and  $V_{CM}$  =  $V_{OUT}$  =  $V_S/2$  (unless otherwise noted)

| Symbol                       | Parameter                             | Conditions                                                                                                                               | Min      | Тур  | Max      | Unit             |

|------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------|------|----------|------------------|

| OFFSE                        | Γ VOLTAGE                             |                                                                                                                                          |          |      |          |                  |

| .,                           |                                       | V <sub>S</sub> = 5 V                                                                                                                     |          | ±0.4 | ±2       | ,,,              |

| Vos                          | Input offset voltage                  | V <sub>S</sub> = 5 V, T <sub>A</sub> = -40°C to 125°C                                                                                    |          |      | ±2.5     | mV               |

| dV <sub>OS</sub> /dT         | V <sub>OS</sub> vs temperature        | T <sub>A</sub> = -40°C to 125°C                                                                                                          |          | ±0.6 |          | μV/°C            |

| PSRR                         | Power-supply rejection ratio          | Vs = 1.8 to 5.5 V, V <sub>CM</sub> = (V-)                                                                                                | 80       | 105  |          | dB               |

| INPUT \                      | OLTAGE RANGE                          |                                                                                                                                          |          |      |          |                  |

| V <sub>СМ</sub>              | Common-mode<br>voltage range          | No phase reversal,<br>rail-to-rail input                                                                                                 | (V-)-0.1 |      | (V+)+0.1 | V                |

|                              |                                       | $V_S = 1.8 \text{ V},$ $(V-) - 0.1 \text{ V} < V_{CM} < (V+) - 1.4 \text{ V},$ $T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}$       |          | 86   |          |                  |

| CMRR                         | Common-mode<br>rejection ratio        | $V_S = 5.5 \text{ V},$<br>$(V-) - 0.1 \text{ V} < V_{CM} < (V+) - 1.4 \text{ V},$<br>$T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ |          | 95   |          | - dB             |

|                              |                                       | $V_S = 5.5 \text{ V},$<br>$(V-) -0.1 \text{ V} < V_{CM} < (V+) + 0.1 \text{ V},$<br>$T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}$  |          | 77   |          |                  |

|                              |                                       | $V_S = 1.8 \text{ V},$<br>$(V-) - 0.1 \text{ V} < V_{CM} < (V+) + 0.1 \text{ V},$<br>$T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ |          | 68   |          |                  |

| INPUT E                      | BIAS CURRENT                          |                                                                                                                                          |          |      | '        |                  |

| I <sub>B</sub>               | Input bias current                    | V <sub>S</sub> = 5 V                                                                                                                     |          | ±5   |          | pА               |

| los                          | Input offset current                  |                                                                                                                                          |          | ±2   |          | pА               |

| NOISE                        |                                       |                                                                                                                                          |          |      |          |                  |

| En                           | Input voltage noise<br>(peak to peak) | f = 0.1 Hz to 10 Hz, Vs = 5 V                                                                                                            |          | 4.7  |          | μV <sub>PP</sub> |

| _                            | Input voltage                         | $f = 1 \text{ kHz}, V_S = 5 \text{ V}$                                                                                                   |          | 30   |          |                  |

| e <sub>n</sub> noise density |                                       | f = 10 kHz, V <sub>S</sub> = 5 V                                                                                                         |          | 27   |          | nV/√Hz           |

| i <sub>n</sub>               | Input current noise density (2)       | f = 1 kHz, V <sub>S</sub> = 5 V                                                                                                          |          | 23   |          | fA/√Hz           |

| INPUT (                      | CAPACITANCE (2)                       |                                                                                                                                          |          |      |          |                  |

| C <sub>ID</sub>              | Differential                          |                                                                                                                                          |          | 1.5  |          | pF               |

| C <sub>IC</sub>              | Common-mode                           |                                                                                                                                          |          | 5    |          | pF               |

## **Electrical Characteristics (Continued)**

| Symbol                                  | Parameter              | Conditions                                                    | Min        | Тур      | Max         | Unit  |  |

|-----------------------------------------|------------------------|---------------------------------------------------------------|------------|----------|-------------|-------|--|

| OPEN-LOOP GAIN                          |                        |                                                               |            |          |             |       |  |

|                                         |                        | $V_S = 5.5 \text{ V}, R_L = 10 \text{ k}\Omega$               | 104        | 117      |             |       |  |

|                                         |                        | $(V-) + 0.05 V < V_0 < (V+) - 0.05 V$                         | 104        | 117      |             |       |  |

|                                         |                        | $V_S = 1.8 \text{ V}, R_L = 10 \text{ k}\Omega$               |            | 100      |             |       |  |

| A <sub>VO</sub>                         | Open-loop              | $(V-) + 0.04 V < V_0 < (V+) - 0.04 V$                         |            | 100      |             | dB    |  |

| Avo                                     | voltage gain           | $V_{S} = 1.8 \text{ V}, R_{L} = 2 \text{ k}\Omega$            |            | 115      |             |       |  |

|                                         |                        | $(V-) + 0.1 V < V_0 < (V+) - 0.1 V$                           |            | 110      |             |       |  |

|                                         |                        | $V_S = 5.5 \text{ V}, R_L = 2 \text{ k}\Omega$                |            | 130      |             |       |  |

|                                         |                        | $(V-) + 0.15 V < V_0 < (V+) - 0.15 V$                         |            | 130      |             |       |  |

| FREQU                                   | ENCY RESPONSE          |                                                               |            |          |             |       |  |

| GBW                                     | Gain-bandwidth product | V <sub>S</sub> = 5 V                                          |            | 1        |             | MHz   |  |

| φm                                      | Phase margin           | V <sub>S</sub> = 5 V, G = 1                                   |            | 78       |             | 0     |  |

| SR                                      | Slew rate              | V <sub>S</sub> = 5 V                                          |            | 2        |             | V/µs  |  |

|                                         | Settling time (2)      | To 0.1%, V <sub>S</sub> = 5 V, 2V step,                       |            | 2.5      |             | . IIe |  |

| +-                                      |                        | G = +1, C <sub>L</sub> = 100 pF                               |            |          |             |       |  |

| t <sub>s</sub>                          |                        | To 0.01%, V <sub>S</sub> = 5 V, 2V step,                      |            | 3        |             | μs    |  |

|                                         |                        | G = +1, C <sub>L</sub> = 100 pF                               |            | <u> </u> |             |       |  |

| t <sub>OR</sub>                         | Overload               | V <sub>2</sub> = 5 V V <sub>2</sub> × gain > V <sub>2</sub>   |            | 0.85     |             | He    |  |

| UR                                      | recovery time          | V <sub>S</sub> = 5 V, V <sub>IN</sub> × gain > V <sub>S</sub> |            | 0.00     |             | μs    |  |

| THD+N                                   | Total harmonic         | $V_S = 5.5 \text{ V}, V_{CM} = 2.5 \text{ V},$                |            | 0.004    |             | %     |  |

| 1110.11                                 | distortion + noise     | $V_0 = 1 V_{RMS}, G = +1, f = 1 \text{ kHz},$                 | kHz,       |          |             | 70    |  |

| OUTPU                                   | Т                      |                                                               |            |          |             |       |  |

| Vo                                      | Voltage output swing   | $V_S = 5.5 \text{ V}, R_L = 10 \text{ k}\Omega$               |            | 10       | 20          | mV    |  |

| • • • • • • • • • • • • • • • • • • • • | from supply rails      | $V_S = 5.5 \text{ V}, R_L = 2 \text{ k}\Omega$                |            | 35       | 55          | 111 V |  |

| Isc                                     | Short-circuit current  | V <sub>S</sub> = 5.5 V                                        |            | ±40      |             | mA    |  |

| Zo                                      | Open-loop output       | V <sub>S</sub> = 5 V, <i>f</i> = 1 MHz                        |            | 1200     |             | Ω     |  |

|                                         | impedance (2)          |                                                               |            |          |             |       |  |

| POWER                                   | SUPPLY                 | I                                                             | 1          |          |             |       |  |

| Vs                                      | Specified              |                                                               | 1.8 (±0.9) |          | 5.5 (±2.75) | V     |  |

|                                         | voltage range          |                                                               | . ,        |          | , ,         |       |  |

|                                         | Quiescent current      | $I_0 = 0 \text{ mA}, V_S = 5.5 \text{ V}$                     |            | 60       | 85          |       |  |

| IQ                                      | per amplifier          | $I_0 = 0 \text{ mA}, V_S = 5.5 \text{ V},$                    |            |          | 90          | μA    |  |

|                                         |                        | $T_A = -40^{\circ}C \text{ to } 125^{\circ}C$                 |            |          |             |       |  |

Note2: Guaranteed by design.

#### **Application Notes**

#### **Layout Guidelines**

For best operational performance of the device, use good PCB layout practices, including:

Place the external components as close to the device as possible. This configuration prevents parasitic errors (such as the Seebeck effect) from occurring.

To reduce parasitic coupling, run the input traces as far away from the supply lines and digital signal as possible.Low-ESR, 0.1µF ceramic bypass capacitors must be connected between each supply pin and ground, placed as close to the device as possible. A single bypass capacitor from V+ to ground is applicable to single supply applications.

Consider a driven, low-impedance guard ring around the critical traces. A guard ring can significantly reduce leakage currents from nearby traces that are at different potentials.

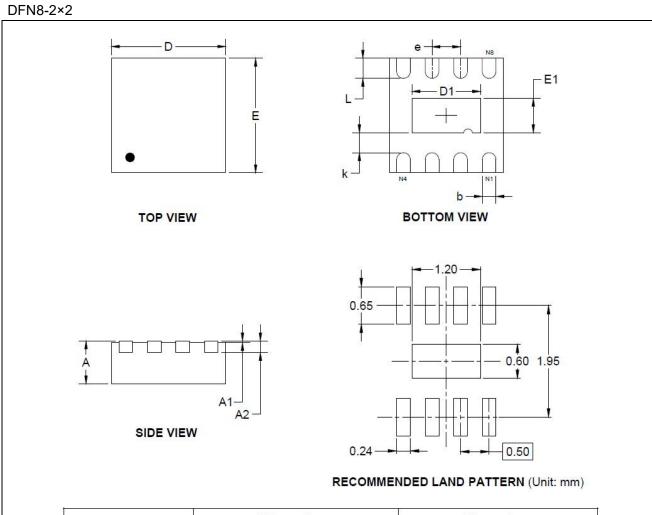

## **Package Dimension**

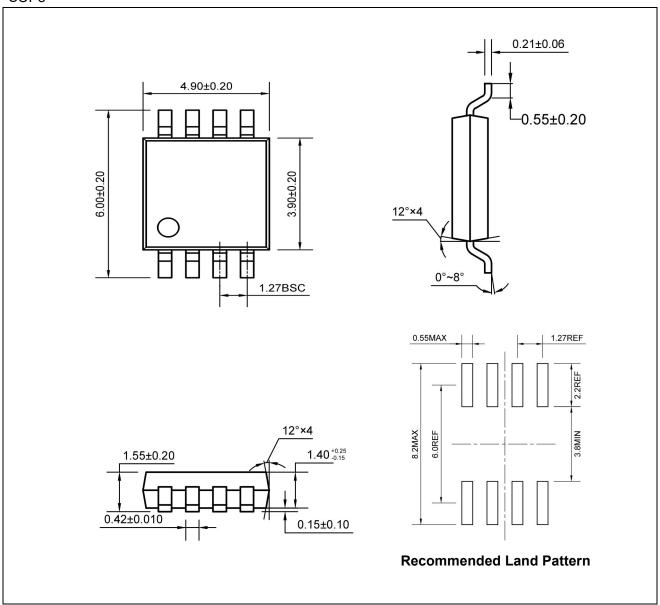

SOP8

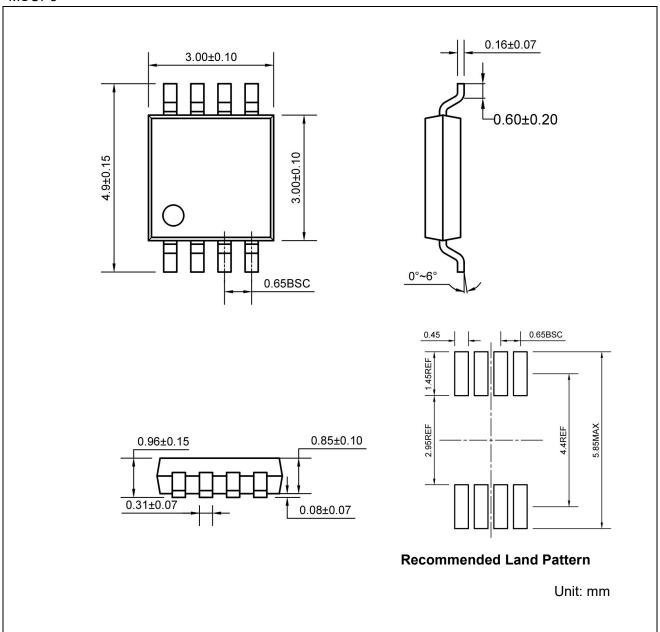

#### MSOP8

| Symbol | Dimensions<br>In Millimeters |       | Dimensions<br>In Inches |       |

|--------|------------------------------|-------|-------------------------|-------|

|        | MIN                          | MAX   | MIN                     | MAX   |

| Α      | 0.700                        | 0.800 | 0.028                   | 0.031 |

| A1     | 0.000                        | 0.050 | 0.000                   | 0.002 |

| A2     | 0.203                        | REF   | 0.008                   | REF   |

| D      | 1.900                        | 2.100 | 0.075                   | 0.083 |

| D1     | 1.100                        | 1.300 | 0.043                   | 0.051 |

| E      | 1.900                        | 2.100 | 0.075                   | 0.083 |

| E1     | 0.500                        | 0.700 | 0.020                   | 0.028 |

| k      | 0.200                        | MIN   | 0.008                   | 3 MIN |

| b      | 0.180                        | 0.300 | 0.007                   | 0.012 |

| е      | 0.500                        | TYP   | 0.020 TYP               |       |

| L      | 0.250                        | 0.450 | 0.010                   | 0.018 |

## **Revision History and Checking Table**

| Version | Date       | Revision Item                | Modifier | Function & Spec<br>Checking | Package & Tape<br>Checking |

|---------|------------|------------------------------|----------|-----------------------------|----------------------------|

| 0.0     | 2022-9-21  | Preliminary Version          | Shibo    | Wanggp                      | Liujy                      |

| 1.0     | 2023-9-27  | Original Version             | Huyt     | Chenh                       | Liujy                      |

| 1.1     | 2024-11-27 | IQ max changed 82uA          | Shibo    | Wanggp                      | Liujy                      |

| 1.2     | 2025-3-24  | Update VOS max<br>and IQ max | Huyt     | Chenh,Tangyx                | Liujy                      |

| 1.3     | 2025-4-11  | Update MSL Grade             | Huyt     | Chenh,Tangyx                | Liujy                      |