## 4A, Low-noise (6µV) Voltage Regulator

### **General Description**

The ET5D001YB is a low-noise ( $6\mu V_{RMS}$ ), low- dropout voltage regulator (LDO) capable of sourcing a 4A load with low dropout. The output voltages are fully user-adjustable using a printed circuit board (PCB) layout without the need of external resistors, thus reducing overall component count. For higher output voltage applications, the device achieves output voltages up to 5V with the use of external resistors. The device supports very low input voltages (down to 1.1V) with the use of an additional BIAS rail.

With very high accuracy, remote sensing, and soft-start capabilities to reduce inrush current, the ET5D001YB is ideal for powering high-current, low-voltage devices such as high-end microprocessors and field-programmable gate arrays.

The ET5D001YB is designed to power-up noise-sensitive components in high-speed communication applications. The very low-noise,  $6\mu V_{RMS}$  device output and high broad-bandwidth PSRR minimizes phase noise and clock jitter in high-frequency signals. These features maximize performance of clocking devices, analog-to-digital converters, and digital-to-analog converters.

#### **Features**

- Ultra low Dropout: 400mV Maximum at 4A

- Output Voltage Noise: 6µV<sub>RMS</sub>

- Power-Supply Ripple Rejection: 40dB at 1MHz

- Input Voltage Range: Without BIAS:1.4V to 5.5V; With BIAS:1.1V to 5.5V

- Two Output Voltage Modes:

- -- Programmable output Version: Output Voltage Range: 0.8V to 3.95V

- -- Adjustable Version: Output Voltage Range: 0.8V to 5.0V

- 1.0% Accuracy Over Line, Load, and Temperature

- Programmable Soft-Start Output

- Power-Good (PG) Output

- Built-in Under Voltage Lockout (UVLO)

- Built-in Internal Current Limit

- Package Information:

| Part No.  | Package     | MSL     |

|-----------|-------------|---------|

| ET5D001YB | QFN20 (5×5) | Level 3 |

1

### **Applications**

• RF, IF Components: VCO, ADC, DAC, LVDS

Wireless Infrastructure: FPGA, DSP

• Test and Measurement

• Instrumentation, Medical, and Audio

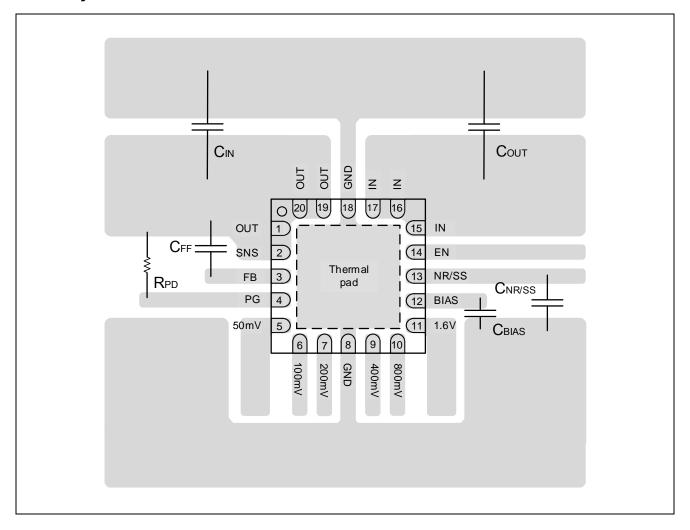

### **Pin Configuration**

### **Pin Function**

| Pin No.       | Pin Name     | Pin Function                                                             |

|---------------|--------------|--------------------------------------------------------------------------|

| 1,19,20       | OUT          | Regulated output pin. A ceramic capacitor is required for stability.     |

| 2             | SNS          | Output voltage sense input pin. Connect this pin only if the             |

|               | 3113         | Programmable output feature is used.                                     |

|               |              | Output voltage feedback pin connected to the error amplifier. Although   |

|               |              | not required, a 10nF feed-forward capacitor from FB to OUT (as close     |

| 3             | FB           | to the device as possible) is recommended for low-noise applications     |

| Ŭ             | 1.5          | to maximize ac performance. The use of a feed-forward capacitor may      |

|               |              | disrupt PG (power good) functionality. See the Programmable Output       |

|               |              | Voltage and Adjustable Operation sections for more details.              |

|               |              | Active-high power-good pin. An open-drain output indicates when the      |

| 4             | PG           | output voltage reaches the target. The use of a feed-forward capacitor   |

|               |              | may disrupt PG functionality.                                            |

|               |              | Output voltage setting pins. Connect these pins to ground or leave       |

|               | 50mV, 100mV, | floating. Connecting these pins to ground increases the output voltage   |

| 5,6,7,9,10,11 | 200mV,       | by the value of the pin name; multiple pins can be simultaneously        |

| 0,0,7,0,10,11 | 400mV,       | connected to GND to select the desired output voltage. Leave these       |

|               | 800mV, 1.6V  | pins floating (open) when not in use. See the Programmable Output        |

|               |              | Voltage section for more details.                                        |

| 8,18 GND      |              | Ground pin.                                                              |

| 12            | BIAS         | BIAS supply voltage pin for the use of 1.1V ≤ IN ≤ 1.4V and to connect   |

| 12            | DI/ (O       | a 10µF capacitor between this pin and ground.                            |

|               |              | Noise-reduction and soft-start pin. Connecting an external capacitor     |

|               |              | between this pin and ground reduces reference voltage noise and          |

| 13            | NR/SS        | also enables the soft-start function. Although not required, a capacitor |

| 10            | 1414/33      | is recommended for low-noise applications to connect a 10nF              |

|               |              | capacitor from NR/SS to GND (as close to the device as possible) to      |

|               |              | maximize ac performance.                                                 |

|               |              | Enable pin. Driving this pin to logic high enables the device; Driving   |

| 14            | EN           | this pin to logic low disables the device. See the Start-Up section for  |

|               |              | more details.                                                            |

| 15,16,17      | IN           | Input supply voltage pin. A 10µF input ceramic capacitor is required.    |

|               | Thermal Pad  | Connect the thermal pad to a large-area ground plane. The thermal        |

|               | Thomas au    | pad is internally connected to GND.                                      |

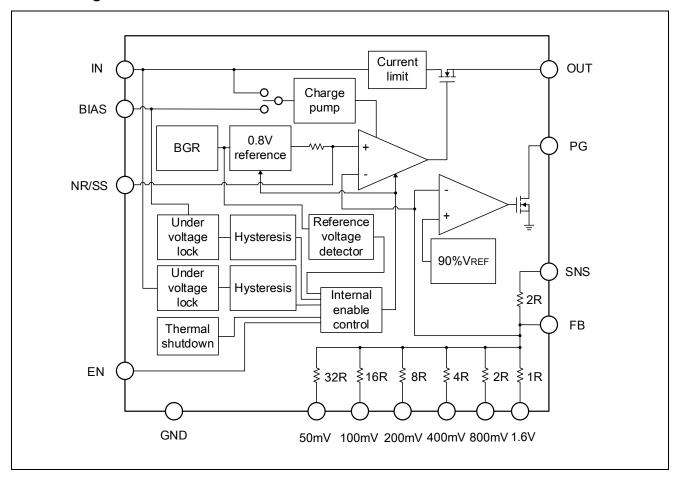

### **Block Diagram**

### **Functional Description**

### Overview

The ET5D001YB is a low-noise, high PSRR, low-dropout regulator capable of sourcing a 4A load with low dropout. The ET5D001YB can operate down to 1.1V input voltage and 0.8V output voltage. This combination of low noise, high PSRR, and low output voltage makes the device an ideal low dropout regulator to power a multitude of loads from noise-sensitive communication components in high-speed communication applications to high-end microprocessors or field-programmable gate array.

The ET5D001YB block diagram contains several features, including:

- With an internal charge pump;

- Low-noise, 0.8V reference;

- Internal protection circuitry: UVLO, Internal current limit, TSD;

- Programmable soft-start;

- Power-good output;

- An integrated resistance network (Programmable output) with a 50mV minimum resolution.

#### **Device Functional Modes**

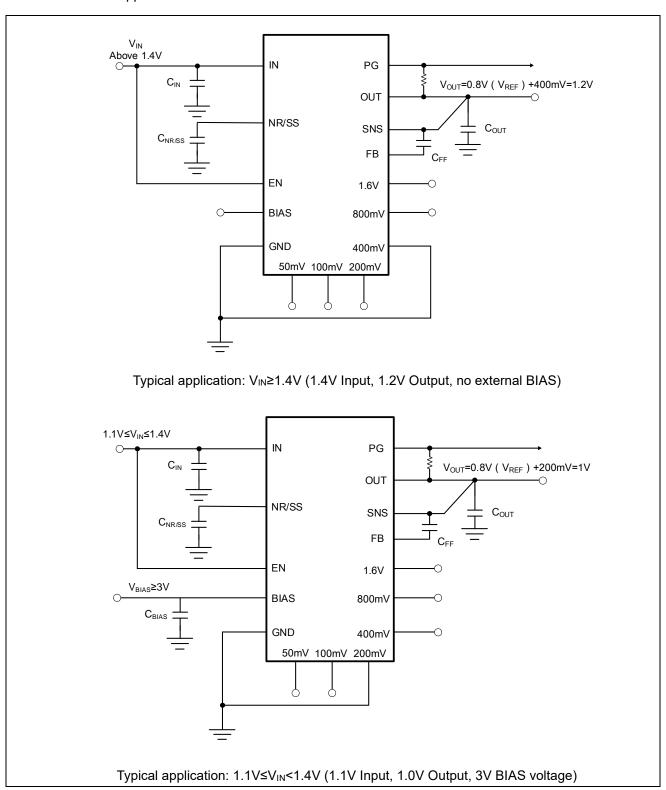

Operation with 1.1V>V<sub>IN</sub>>1.4V

The ET5D001YB requires a bias voltage on the BIAS pin≥3.0V if the high-current input supply voltage is between 1.1V to 1.4V. The bias voltage pin consumes 2.3mA, nominally.

Operation with 1.4V≥V<sub>IN</sub>>5.5V

If the input voltage is equal to, or exceeds 1.4V, no bias voltage is necessary. The device is automatically selected to be powered from the IN pin in this condition and the BIAS pin can be left floating.

#### Disabled

If the voltage on the EN pin is less than 0.5V, the device is disabled and the output is high impedance. The output impedance of the LDO is then set by the gain setting resistors if a path to GND is provided between OUT and GND. In this state, quiescent current does not exceed 2.5µA. Raising EN above 1.1V (maximum) initiates the startup sequence of the device.

#### Start-Up

Enable (EN) and Under voltage Lockout (UVLO)

The ET5D001YB only turns on when both EN and UVLO are above the respective voltage thresholds. The UVLO circuit monitors input and bias voltage ( $V_{IN}$  and  $V_{BIAS}$ , respectively) to prevent device turn-on before  $V_{IN}$  and  $V_{BIAS}$  rise above the lockout voltage. The UVLO circuit also causes a shutdown when  $V_{IN}$  and  $V_{BIAS}$  fall below lockout. The EN signal allows independent logic-level turn-on and shutdown of the LDO. If the device turn-on is required to be controlled, the device must be enabled with or after  $V_{IN}$ . Connect EN to VIN if turn-on control of the output voltage is not needed.

Noise-Reduction and Soft-Start Capacitor (CNR/SS)

The ET5D001YB features a programmable, monotonic, voltage-controlled soft-start that is set with an external capacitor (C<sub>NR/SS</sub>). This soft-start eliminates power-up initialization problems when powering field-programmable gate arrays (FPGAs), digital signal processors (DSPs), or other processors. The controlled voltage ramp of the output also reduces peak inrush current during start-up, minimizing start-up transients to the input power bus.

To achieve a linear and monotonic start-up, the ET5D001YB error amplifier tracks the voltage ramp of the external soft-start capacitor until the voltage exceeds the internal reference. The soft-start ramp time depends on the soft- start charging current ( $I_{NR/SS}$ ), the soft-start capacitance ( $C_{NR/SS}$ ), and the internal reference ( $V_{REF}$ ). Soft- start ramp time can be calculated as followed:

#### $t_{SS} = (V_{REF} \times C_{NR/SS}) / I_{NR/SS}$

Note: That INR/SS is provided in the Electrical Characteristics table and has a typical value of 6.2 µA

For low-noise applications, the noise-reduction capacitor (connected to the NR/SS pin of the LDO) forms an RC filter for filtering out noise that is ordinarily amplified by the control loop and appears on the output voltage. For low-noise applications, a 10nF to  $1\mu$ F  $C_{NR/SS}$  is recommended.

#### Soft-Start and Inrush Current

Soft-start refers to the ramp-up characteristic of the output voltage during LDO turn-on after EN and UVLO achieve threshold voltage. The noise-reduction capacitor serves a dual purpose of both governing output noise reduction and programming the soft-start ramp during turn-on.

Inrush current is defined as the current into the LDO at the IN pin during start-up. Inrush current then consists primarily of the sum of load and current used to charge the output capacitor. This current is difficult to measure because the input capacitor must be removed, which is not recommended.

### **Feature Description**

### **Programmable Output Operation**

The ET5D001YB does not require external resistors to set output voltage, which is typical of adjustable low-dropout voltage regulators. However, the ET5D001YB uses pins 5, 6, 7, 9, 10, and 11 to program the regulated output voltage. Each pin is either connected to ground (active) or left open (floating). Programmable output programming is set by Equation 1 as the sum of the internal reference voltage (V<sub>REF</sub>=0.8V) plus the accumulated sum of the respective voltages assigned to each active pin; that is, 50mV (pin5), 100mV (pin6), 200mV (pin7), 400mV (pin9), 800mV (pin10), or 1.6V (pin11). By leaving all program pins open, or floating, the output is thereby programmed to the minimum possible output voltage equal to V<sub>REF</sub>.

### V<sub>OUT</sub>=V<sub>REF</sub>+(∑Pins to Ground)

| PROGRAM PINS (Active Low) | ADDITIVE OUTPUT VOLTAGE LEVEL |  |

|---------------------------|-------------------------------|--|

| Pin 5 (50mV)              | 50mV                          |  |

| Pin 6 (100mV)             | 100mV                         |  |

| Pin 7 (200mV)             | 200mV                         |  |

| Pin 9 (400mV)             | 400mV                         |  |

| Pin 10 (800mV)            | 800mV                         |  |

| Pin 11 (1.6V)             | 1.6V                          |  |

The voltage setting pins have a binary weight; therefore, the output voltage can be programmed to any value from 0.8V to 3.95V in 50mV steps. As followed: Binary 0 means the pin is open, Binary 1 means the pin is connected to GND.

| {1.6V,800mv, 400mv, 200mv, 100mv, 50mv} | Output Voltage(V) |

|-----------------------------------------|-------------------|

| 00_000(default)                         | 0.80              |

| 00_0001                                 | 0.85              |

| 00_0010                                 | 0.90              |

|                                         |                   |

| 10_0000                                 | 2.40              |

| 10_0001                                 | 2.45              |

| 10_0010                                 | 2.50              |

|                                         |                   |

| 11_1101                                 | 3.85              |

| 11_1110                                 | 3.90              |

| 11_1111                                 | 3.95              |

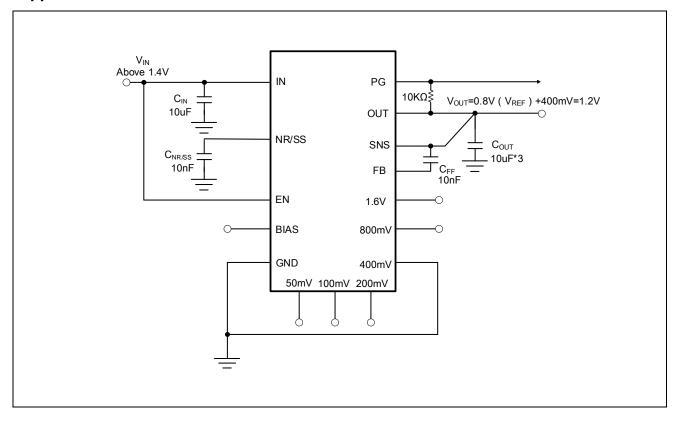

Considering the use of the programmable output internal network, the output voltage is set by grounding the appropriate control pins. When grounded, all control pins add a specific voltage on top of the internal reference voltage ( $V_{REF}$ =0.8V). The followed figures show a 1.2V and 1V output voltage, respectively, that provide an example of the circuit usage with and without BIAS voltage. These schematics are described in more detail in the Application Circuits.

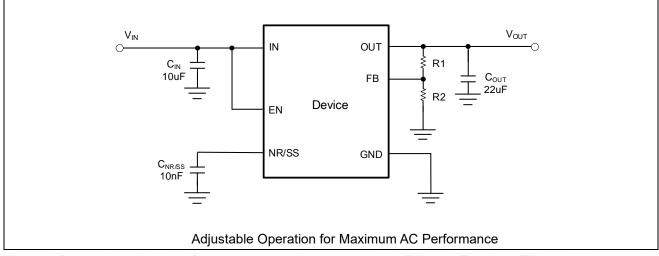

#### **Adjustable Operation**

The ET5D001YB can be used either with the internal programmable output network or using external resistors. Using the programmable output network allows the ET5D001YB to be programmed from 0.8V to 3.95V. To extend this range of output voltage operation to 5.0V, external resistors must be used. This configuration is referred to as the adjustable configuration of the ET5D001YB throughout this document. Regardless whether the internal resistor network or whether external resistors are used, the nominal output voltage of the device is set by two resistors. Using an internal resistor ensures a 1% matching and minimizes both the number of external components and layout footprint.

R1 and R2 can be calculated for any output voltage range using followed Equation. This resistive network must provide a current equal to or greater than  $5\mu$ A for optimum noise performance.

$$R_1 = R_2 \left( rac{V_{OUT}}{V_{REF}} - 1

ight)$$

, where ,  $rac{|V_{REF(max)}|}{R_2} > 5 \mu A$

The followed table shows the resistor combination required to achieve a few of the most common rails using commercially-available, 0.1%-tolerance resistors to maximize nominal voltage accuracy while abiding to the formula shown in. Recommended feedback resistor values (R1+R2) <150K $\Omega$ .

#### 4A LDO with an Internal Charge Pump

The ET5D001YB can be used either with the internal resistor network provided, or with the external component as a traditional adjustable LDO. Regardless of the implementation, the ET5D001YB provides excellent regulation to 1% accuracy, excellent dropout voltage, and high output current capability.

If the input voltage is below 1.4V, an external BIAS voltage must be supplied to maintain the dropout characteristics. The input voltage or the BIAS voltage is fed through to an internal charge pump to power the internal error amplifier providing the regulation.

The internal charge pump ensures proper operation without requiring an external BIAS voltage down to +1.4V input voltage. Below a 1.4V input voltage, a BIAS input voltage between 3.0V and 5.5V is required.

#### Low-Noise, 0.8-V Reference

The ET5D001YB includes a low-noise reference ensuring minimal noise during operation because the internal reference is normally the dominant term in noise analysis. Further noise reduction can be achieved using the NR/SS pin and by adding an external C<sub>FF</sub> between the SNS pin and the FB pin.

### **Under voltage Lockout (UVLO)**

The under voltage lockout (UVLO) circuit monitors the input and bias voltage (V<sub>IN</sub> and V<sub>BIAS</sub>, respectively) to prevent the device from turning on before VIN and VBIAS rise above the lockout voltage. The UVLO circuit also causes a shutdown when V<sub>IN</sub> and V<sub>BIAS</sub> fall below the lockout voltage.

#### Internal Current Limit (ILIMIT)

The internal current limit circuit is used to protect the LDO against high-load current faults or shorting events. The LDO is not designed to operate in a steady-state current limit. During a current-limit event, the LDO sources constant current. Therefore, the output voltage falls when load impedance decreases. Note also that if a current limit occurs and the resulting output voltage is low, excessive power may be dissipated across the LDO, resulting in a thermal shutdown of the output.

A fold back feature limits the short-circuit current to protect the regulator from damage under all load conditions. If OUT is forced below 0 V before EN goes high and the load current required exceeds the fold back current limit, the device does not start up. In applications that function with both a positive and negative voltage supply, there are several ways to ensure proper start-up:

- Enable the ET5D001YB first and disable the device last.

- Delaying the EN voltage with respect to the IN voltage allows the internal pull-down resistor to discharge any residual voltage at OUT. If a faster discharge rate is required, use an external resistor from OUT to GND.

### **Thermal Shutdown Protection (TSD)**

Thermal shutdown disables the output when the junction temperature rises to approximately 160°C which allows the device to cool. When the junction temperature cools to approximately 140°C, the output circuitry enables. Based on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This thermal cycling limits the dissipation of the regulator and protects it from damage as a result of overheating.

The thermal shutdown circuitry of the ET5D001YB has been designed to protect against temporary thermal overload conditions. The TSD circuitry was not intended to replace proper heat-sinking. Continuously running the ET5D001YB device into thermal shutdown may degrade device reliability

#### **Programmable Soft-Start**

Soft-start refers to the ramp-up characteristic of the output voltage during LDO turn-on after EN and UVLO exceed the respective threshold voltage. The noise-reduction capacitor (C<sub>NR/SS</sub>) serves a dual purpose of both governing output noise reduction and programming the soft-start ramp during turn-on.

#### **Power-Good Function**

The ET5D001YB has a power-good function that works by toggling the state of the PG output pin. When the output voltage falls below the PG threshold voltage, the PG pin open-drain output engages (low impedance to GND). When the output voltage exceeds the PG threshold voltage by an amount greater than VHYS (PG), the PG pin becomes high-impedance. By connecting a pull-up resistor to an external supply, any downstream device can receive PG as a logic signal. Make sure that the external pull-up supply voltage results in a valid logic signal for the receiving device or devices. Use a pull-up resistor from  $10k\Omega$  to  $100k\Omega$  for best results.

When employing the feed-forward capacitor (C<sub>FF</sub>), the turn-on time-constant for the LDO is increased and the power-good output time-constant stays the same, resulting in an invalid status of the LDO. To avoid this issue and receive a valid PG output, ensure that the time-constant of both the LDO and the power-good output match.

#### **Capacitor Recommendation**

The ET5D001YB is designed to be stable using low equivalent series resistance (ESR) ceramic capacitors at the input, output, and noise-reduction pin (NR, pin13). Ceramic capacitors that employ X7R, X5R, and COG rated dielectric materials provide relatively good capacitive stability across temperature.

Input and Output Capacitor Requirements (C<sub>IN</sub> and C<sub>OUT</sub>)

The ET5D001YB is designed and characterized for operation with ceramic capacitors of 22µF or greater at the output and 10µF at the input. Locate the input and output capacitors as near as practical to the respective input and output pins.

Feed-Forward Capacitor (C<sub>FF</sub>)

Although a feed-forward capacitor ( $C_{FF}$ ), from the FB pin to the OUT pin is not required to achieve stability, a 10nF, feed-forward capacitor optimizes the noise and PSRR performance. A higher capacitance  $C_{FF}$  can be used; However, the startup time is longer and the power-good signal may incorrectly indicate the output voltage has settled.

## **Absolute Maximum Ratings**

| Symbol                              | Parameters (Items)                     |             | Value                         | Unit |  |

|-------------------------------------|----------------------------------------|-------------|-------------------------------|------|--|

| VIN/VBIAS/VPG/VEN                   | IN, BIAS, PG, EN Voltage               |             | -0.3 to 6                     | V    |  |

| V <sub>SNS</sub> /V <sub>OUT</sub>  | SNS, Output Voltag                     | е           | -0.3 to V <sub>IN</sub> +0.3  | V    |  |

| V <sub>NR/SS</sub> /V <sub>FB</sub> | NR/SS, FB Output Vol                   | tage        | -0.3 to 3.6                   | V    |  |

| VOTHER_PINS                         | 50mV, 100mV, 200mV, 400mV, Voltage     | 800mV, 1.6V | -0.3 to V <sub>ОUТ</sub> +0.3 | V    |  |

| IOUT_MAX                            | Maximum Load Curre                     | ent         | 4000                          | mA   |  |

| I <sub>PG_MAX</sub>                 | PG (sink current into de               | evice)      | 5                             | mA   |  |

| P <sub>D</sub>                      | Maximum Power Consumption              | QFN20(5*5)  | 2000                          | mW   |  |

| V                                   | Human Body Model (JESD22-A114)         |             | ±2000                         | V    |  |

| V <sub>ESD</sub>                    | Charged Device Model (JESD22-C101)     |             | ±2000                         | V    |  |

| Reja                                | Junction-to-ambient Thermal Resistance |             | 62.5                          | °C/W |  |

| TJ                                  | Operating Junction Temperature         |             | -40 to 150                    | °C   |  |

| T <sub>STG</sub>                    | Storage Temperature                    |             | -65 to 150                    | °C   |  |

| T <sub>SLOD</sub>                   | Lead Temperature (Soldering, 10 sec)   |             | 300                           | °C   |  |

## **Recommended Operating Conditions**

| Symbol            | Parameters                                   | Rating     | Unit  |

|-------------------|----------------------------------------------|------------|-------|

| V <sub>IN</sub>   | Input Voltage                                | 1.1 to 5.5 | V     |

| $V_{BIAS}$        | Supply Bias Voltage                          | 3.0 to 5.5 | V     |

| I <sub>OUT</sub>  | Output Current                               | 0 to 4000  | mA    |

| T <sub>A</sub>    | Operating Ambient Temperature                | -40 to 85  | °C    |

| CIN               | Effective Input Ceramic Capacitor Value      | Min 10     | μF    |

| C <sub>BIAS</sub> | Effective Input Ceramic Capacitor Value      | Min 10     | μF    |

| C <sub>OUT</sub>  | Effective Output Ceramic Capacitor Value     | Min 22     | μF    |

| ESR               | Input and Output Capacitor Equivalent Series | 5 to 100   | mΩ    |

| ESK               | Resistance (ESR)                             | 3 10 100   | 11177 |

### **Electrical Characteristics**

Over operating temperature range (T<sub>J</sub>=-40°C to 125°C),  $\{1.1V \le V_{IN} < 1.4V \text{ and } 3.0V \le V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} = 0.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} = 0.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} = 0.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} = 0.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} = 0.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } 0.5V\}$  or  $\{V_{IN} \ge 1.4V \text{$

| Symbol                  | Parameters                         | Conditions                                                                                                                           | Min      | Тур    | Max                    | Unit |

|-------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------|--------|------------------------|------|

| VIN                     | Input Voltage Range                |                                                                                                                                      | 1.1      |        | 5.5                    | V    |

| V <sub>BIAS</sub>       | Bias supply voltage <sup>(1)</sup> |                                                                                                                                      | 3.0      |        | 5.5                    | V    |

| V <sub>REF</sub>        | Reference voltage                  | V <sub>REF</sub> =V <sub>FB</sub> =V <sub>NR/SS</sub>                                                                                |          | 0.8    |                        | V    |

| V <sub>UVLO1(IN)</sub>  | Input supply UVLO<br>with BIAS     | V <sub>IN</sub> increasing                                                                                                           |          | 1.02   | 1.085                  | V    |

| V <sub>HYS1(IN)</sub>   | V <sub>UVLO1(IN)</sub> hysteresis  | V <sub>IN</sub> falling                                                                                                              |          | 0.2    |                        | mV   |

| Vuvlo2(IN)              | Input supply UVLO without BIAS     | V <sub>IN</sub> increasing                                                                                                           |          | 1.25   | 1.35                   | V    |

| V <sub>HYS2(IN)</sub>   | V <sub>UVLO2(IN)</sub> hysteresis  | V <sub>IN</sub> falling                                                                                                              |          | 250    |                        | mV   |

| V <sub>UVLO(BIAS)</sub> | Bias supply UVLO                   | V <sub>BIAS</sub> increasing                                                                                                         |          | 2.83   | 2.9                    | V    |

| V <sub>HYS(BIAS)</sub>  | V <sub>UVLO(BIAS)</sub> hysteresis | V <sub>BIAS</sub> falling                                                                                                            |          | 290    |                        | mV   |

|                         |                                    | Using voltage setting pins(50mV, 100mV,                                                                                              |          |        |                        |      |

|                         | Output voltage                     | 200mV, 400mV,                                                                                                                        | 0.8-1.0% |        | 3.95+1.0% <sub>V</sub> | V    |

| $V_{OUT}$               |                                    | 800mV, and 1.6V)                                                                                                                     |          |        |                        | -    |

|                         |                                    | Using external resistors                                                                                                             | 0.8-1.0% |        | 5.0+1.0%               |      |

|                         | Output voltage                     | 0.8V≤V <sub>0∪T</sub> ≤5V,<br>5mA≤I <sub>0∪T</sub> ≤4A                                                                               | -1.0%    |        | 1.0%                   |      |

|                         | Accuracy <sup>(4)(5)</sup>         | V <sub>IN</sub> =1.5V, V <sub>OUT</sub> =1.2V,<br>5mA≤I <sub>OUT</sub> ≤1.2A                                                         | -1.0%    |        | 1.0%                   |      |

| ^ <b>\</b> /            | Output Voltage Line<br>Regulation  | V <sub>IN</sub> =1.4V to 5.5V,<br>I <sub>OUT</sub> =5mA                                                                              |          | 0.003  |                        | %/V  |

| $	riangle V_OUT$        | Output Voltage Load<br>Regulation  | I <sub>OUT</sub> from 5mA to 4000mA                                                                                                  |          | 0.0001 |                        | %/A  |

|                         |                                    | V <sub>IN</sub> =1.4V and V <sub>BIAS</sub> open,<br>I <sub>OUT</sub> =4A, V <sub>FB</sub> =0.8V-3%                                  |          | 210    | 450                    |      |

| $V_{DROP}$              | Dropout Voltage                    | V <sub>IN</sub> =1.1V, V <sub>BIAS</sub> =5.0V,<br>V <sub>OUT(TARGET)</sub> =0.8V,<br>I <sub>OUT</sub> =4A, V <sub>FB</sub> =0.8V-3% |          | 170    | 400                    | mV   |

| ILIMIT Current Limit    |                                    | Vout forced at 0.9×Vout(target), Vin=Vout(target)+500mV                                                                              | 4200     | 5200   | 6200                   | mA   |

### **Electrical Characteristics (Continued)**

Over operating temperature range (T<sub>J</sub>=-40°C to 125°C),  $\{1.1V \le V_{IN} < 1.4V \text{ and } 3.0V \le V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$  or  $\{V_{IN} \ge 1.4V \text{ and } V_{BIAS} \le 5.5V\}$

| Symbol                     | Parameters                      | Conditions                                                                                                                                      | Min       | Тур       | Max       | Unit |

|----------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----------|------|

|                            |                                 | Minimum load, V <sub>IN</sub> =5.5V, no V <sub>BIAS</sub> supply, I <sub>OUT</sub> =5mA                                                         |           | 2.8       | 4         |      |

| Ignd                       | GND pin current                 | Maximum load, V <sub>IN</sub> =1.4V, no V <sub>BIAS</sub> supply, I <sub>OUT</sub> =4A                                                          | 3.7       | 5         | mA        |      |

|                            |                                 | Shutdown, PG=(open), $V_{\text{IN}}$ =4.3V, no $V_{\text{BIAS}}$ supply, $V_{\text{EN}}$ =0V                                                    |           |           | 2.5       | μA   |

| I <sub>EN</sub>            | EN pin input current            | $V_{\text{IN}}$ =5.5V, no $V_{\text{BIAS}}$ supply, $V_{\text{EN}}$ =0V and 5.5V                                                                | -0.1      |           | 0.1       | μΑ   |

| Івіаѕ                      | BIAS pin current                | V <sub>IN</sub> =1.1V, V <sub>BIAS</sub> =5.5V,<br>Vout(target)=0.8V,<br>Iout=4A                                                                |           | 2.3       | 3.5       | mA   |

| $V_{IL(EN)}$               | EN Low Threshold                | V <sub>EN</sub> falling from 1.2V                                                                                                               | 0         |           | 0.5       | V    |

| $V_{\text{IH}(\text{EN})}$ | EN High Threshold               | V <sub>EN</sub> increasing from 0V                                                                                                              | 1.1       |           | 5.5       | V    |

| $V_{\text{IT}(PG)}$        | PG pin threshold                | For the direction PG with decreasing V <sub>OUT</sub>                                                                                           | 0.82*Vоит | 0.87*Vоит | 0.93*Vоит | V    |

| V <sub>HYS(PG)</sub>       | PG pin hysteresis               |                                                                                                                                                 |           | 0.02*Vout |           | V    |

| V <sub>OL(PG)</sub>        | PG pin low-level output voltage | V <sub>OUT</sub> <v<sub>IT(PG), I<sub>PG</sub>=-1mA<br/>(current into device)</v<sub>                                                           |           |           | 0.4       | V    |

| ILEAK(PG)                  | PG pin leakage<br>current       | Vout>Vit(PG), V(PG)=5.5V                                                                                                                        |           |           | 1         | μΑ   |

| I <sub>NR/SS</sub>         | NR/SS pin charging current      | V <sub>NR/SS</sub> =GND, V <sub>IN</sub> =5.5V                                                                                                  | 4.0       | 6.2       | 9.0       | μΑ   |

| I <sub>FB</sub>            | FB pin leakage<br>current       | V <sub>IN</sub> =5.5V                                                                                                                           | -100      |           | 100       | nA   |

| PSRR                       | Power Supply<br>Rejection Ratio | f=1MHz, $V_{IN}$ =3.8V,<br>$V_{OUT}$ =3.3V, $I_{OUT}$ =4A,<br>$C_{NR/SS}$ =10nF, $C_{FF}$ =10nF                                                 |           | 40        |           | dB   |

| ем                         | Output noise                    | f=10Hz to 100kHz,<br>$V_{\text{IN}}$ =1.4V, $V_{\text{OUT}}$ =0.8V,<br>$I_{\text{OUT}}$ =4A, $C_{\text{NR/SS}}$ =10nF,<br>$C_{\text{FF}}$ =10nF |           | 6         |           | μV   |

| T <sub>TSD</sub>           | Over-temperature                | T <sub>J</sub> rising                                                                                                                           |           | 160       |           | °C   |

|                            | Shutdown Threshold              | TJ falling from shutdown                                                                                                                        |           | 140       |           | °C   |

**Note1:** BIAS supply is required when the VIN supply is below 1.4V. Conversely, no BIAS supply is needed when the  $V_{IN}$  supply is higher than or equal to 1.4 V.

**Note2:**  $V_{OUT\ (TARGET)}$  is the calculated  $V_{OUT}$  target value from the output voltage setting pins: 50mV, 100mV, 200mV, 400mV, 800mV, and 1.6V in a fixed configuration. In an adjustable configuration,  $V_{OUT\ (TARGET)}$  is the expected  $V_{OUT}$  value set by the external feedback resistors.

**Note3:** This  $50\Omega$  load is disconnected when the test conditions specify an  $I_{OUT}$  value.

**Note4:** When the device is connected to external feedback resistors at the FB pin, external resistor tolerances are not included.

**Note5:** The device is not tested under conditions where  $V_{IN}>V_{OUT}+2.5V$  and  $I_{OUT}=4A$ , because the power dissipation is higher than the maximum rating of the package. Also, this accuracy specification does not apply on any application condition that exceeds the power dissipation limit of the package under test.

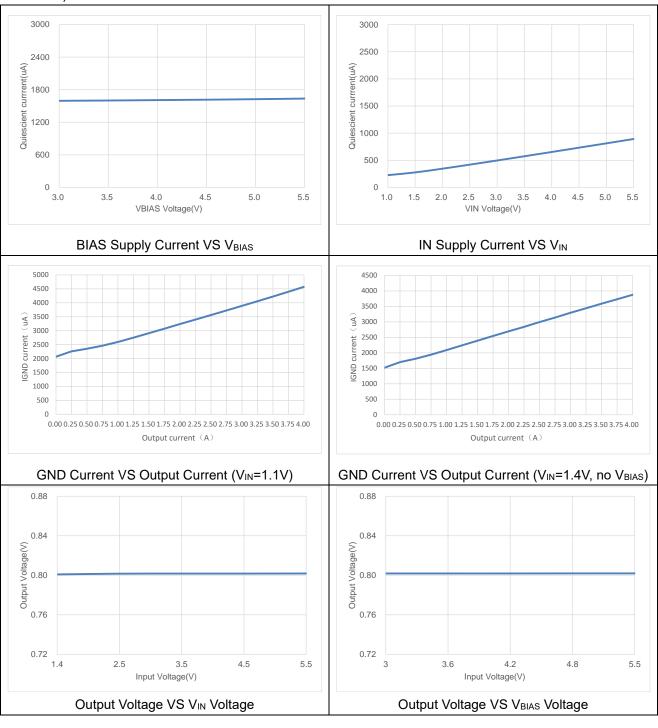

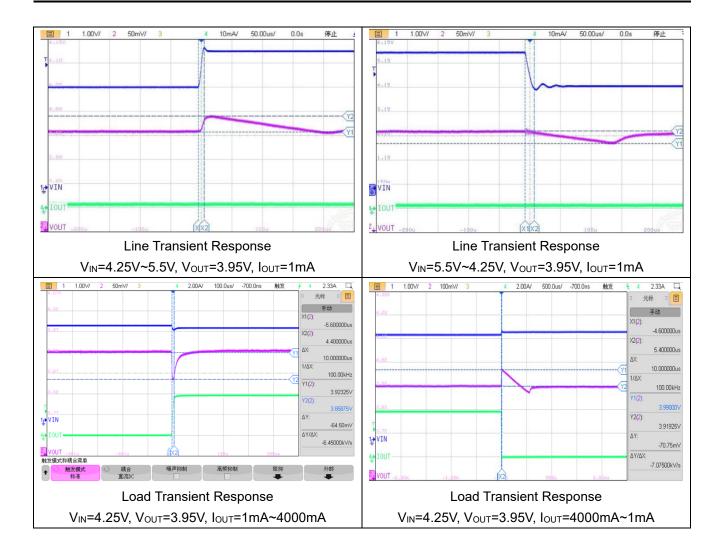

### **Typical Characteristics**

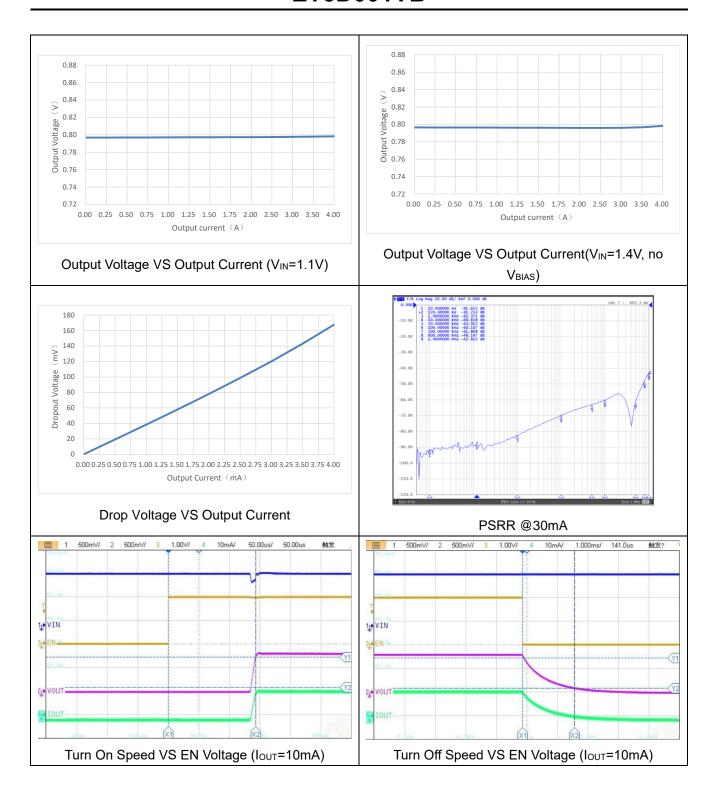

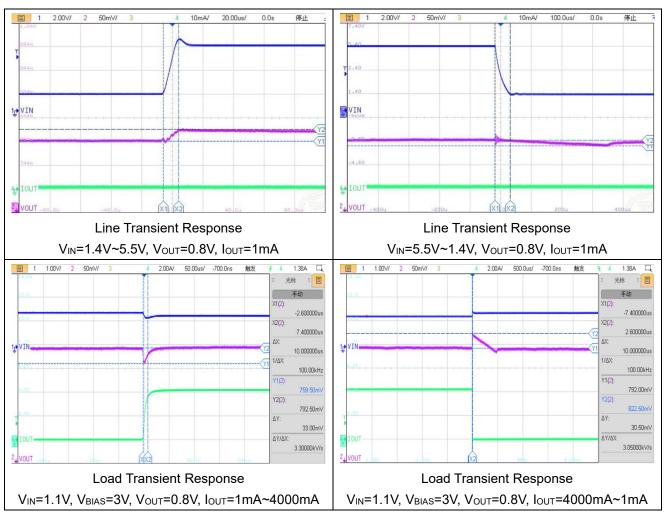

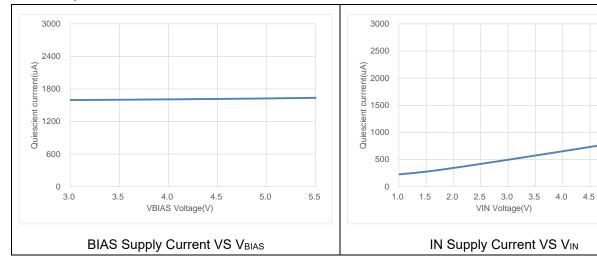

### (1) VOLTAGE VERSION 0.8 V

( $V_{IN}$ =1.1V,  $V_{BIAS}$ =3.0V,  $I_{OUT}$ =1mA,  $C_{IN}$ = $C_{BIAS}$ =10uF,  $C_{OUT}$ =22 $\mu$ F, unless otherwise noted. Typical values are at  $T_A$ =25°C.)

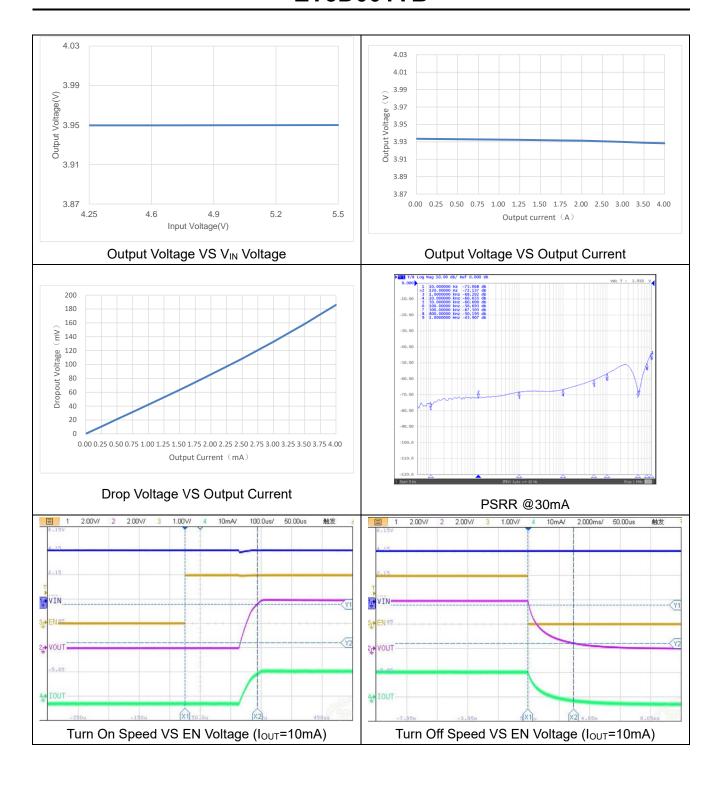

### (2) VOLTAGE VERSION 3.95 V

( $V_{IN}$ =4.25V, no  $V_{BIAS}$ ,  $I_{OUT}$ =1mA,  $C_{IN}$ = $C_{BIAS}$ =10uF,  $C_{OUT}$ =22 $\mu$ F, unless otherwise noted. Typical values are at  $T_A$ =25°C.)

17 Rev 1.2

5.0

5.5

## **Application Circuits**

## **PCB Layout Guide**

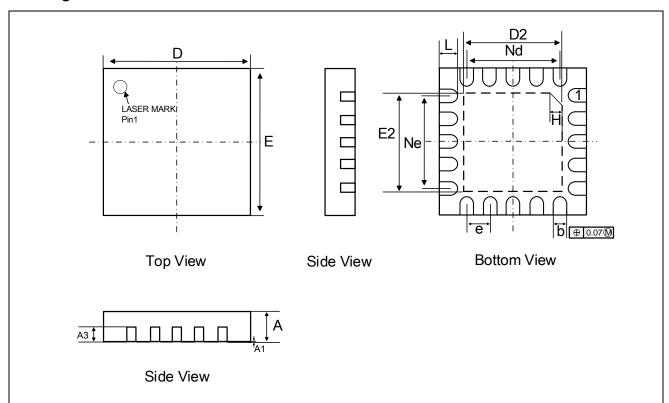

## Package Dimension

| QFN20-5mm*5mm |                |                                                       |      |  |  |

|---------------|----------------|-------------------------------------------------------|------|--|--|

| Cumbal        | Unit: mm       |                                                       |      |  |  |

| Symbol        | Min            | Nom                                                   | Max  |  |  |

| Α             | 0.70           | 0.75                                                  | 0.80 |  |  |

| A1            | -              | 0.02                                                  | 0.05 |  |  |

| A3            | 0.18           | 0.20                                                  | 0.25 |  |  |

| b             | 0.25           | 0.25 0.30                                             |      |  |  |

| D             | 4.90           | 4.90     5.00       4.90     5.00       3.05     3.15 |      |  |  |

| Е             | 4.90           |                                                       |      |  |  |

| D2            | 3.05           |                                                       |      |  |  |

| E2            | 3.05           | 3.15                                                  | 3.25 |  |  |

| Nd            |                | 2.60BSC                                               |      |  |  |

| Ne            |                | 2.60BSC                                               |      |  |  |

| е             | 0.65BSC        |                                                       |      |  |  |

| L             | 0.45 0.55 0.65 |                                                       |      |  |  |

| Н             | 0.30 0.35 0.40 |                                                       |      |  |  |

## **Revision History and Checking Table**

| • | Version | Date       | Revision Item               | Modifier     | Function & Spec<br>Checking | Package & Tape<br>Checking |

|---|---------|------------|-----------------------------|--------------|-----------------------------|----------------------------|

|   | 1.0     | 2023-02-08 | Original Version            | Li Huan      | Liu Yi Guo                  | Li Huan                    |

|   | 1.1     | 2023-04-01 | Update Typeset              | Yang Xiao Xu | Liu Yi Guo                  | Yang Xiao Xu               |

|   | 1.2     | 2024-11-11 | Update characteristic curve | Yang Xiao Xu | Liu Yi Guo                  | Yang Xiao Xu               |